# FE50MKIR FE50MKNR

# DC-50 Fiber Optic OptoLock Transceiver

#### **DESCRIPTION**

The Firecomms DC-50 MBd OptoLock ® transceiver consists of a highly reliable Resonant Cavity Light Emitting Diode (RCLED) with integrated driver IC as a visible optical transmitter and a receiver with a fully integrated photodiode and receiver IC. They are housed in Firecomms patented OptoLock® for fast simple termination of Plastic Optic Fiber (POF). They are capable of sending 50 Mbps digital signals over fiber and operate in the temperature range of -40 °C to +85 °C. The device can operate from 5 V or 3.3 V DC power supply rails.

The transmitter contains a red wavelength RCLED with fully integrated precision driver IC, designed to provide a communication link over POF. The RCLED in this transceiver is a highly reliable visible incoherent light source requiring low operating current. The use of intrinsically eye-safe, visible light simplifies link set-up and testing. The transmitter has a non-inverting optical output.

The receiver is a robust optical to electrical receiver with integrated pulse width distortion minimization circuitry for reliable data transmission. The receiver features a push-pull TTL compatible CMOS output. The receiver is available in inverting and non-inverting options.

#### **AVAILABLE OPTIONS**

Table 1

ORDERING INFORMATION / PART NUMBERS

| DC-50 Mb Optolock<br>Non-Inverting Tx, Inverting Rx     | FE50MKIR |

|---------------------------------------------------------|----------|

| DC-50 Mb Optolock<br>Non-Inverting Tx, Non-Inverting Rx | FE50MKNR |

#### **FEATURES**

- Visible RCLED at red wavelength (650 nm)

- Optimized for data transmission from DC to 50 MBd

- Industrial temperature range -40 °C to +85 °C

- Push Pull TTL Compatible CMOS output

- Dual 5 V and 3.3 V power supply

- RoHS compliant and flame retardant

- (UL 94 V-0) connector housings

- Ultra-low pulse width distortion suitable for burst mode data transmission

#### **APPLICATIONS**

# Table 2 APPLICATIONS

| Application | Automation and Industrial Control. Serial Communications. Voltage Isolation. |

|-------------|------------------------------------------------------------------------------|

| Standard    | Serial RS232, RS485, CAN-Bus,<br>MODBUS, Profibus                            |

| Distance    | 50 meters Step Index POF [1]                                                 |

| Speed       | DC to 50 MBd                                                                 |

|             |                                                                              |

Note: 1. Depending on the installation conditions

OptoLock® products are protected by European patent EP 2035874, U.S. patents 7,597,485 and 7,905,665, Chinese patents 101501545 A and 102135650 B.

Table 3

TRANSCEIVER PIN DESCRIPTION

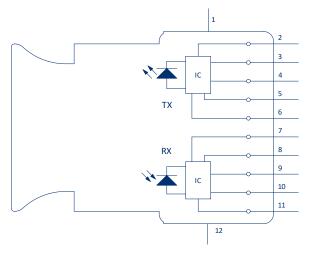

| Pin | Name Symbol       |      |  |  |

|-----|-------------------|------|--|--|

|     | Transmitter       |      |  |  |

| 1   | EMI Shield [1]    | GND  |  |  |

| 2   | Data Input (TTL)  | Vin  |  |  |

| 3   | Ground            | GND  |  |  |

| 4   | Ground            | GND  |  |  |

| 5   | Vcc (5/3.3 V) [2] | Vcc  |  |  |

| 6   | Vcc (5/3.3 V)     | Vcc  |  |  |

|     | Receiver          |      |  |  |

| 7   | Vcc (5/3.3 V)     | Vcc  |  |  |

| 8   | Vcc (5/3.3 V)     | Vcc  |  |  |

| 9   | Ground            | GND  |  |  |

| 10  | Data Output       | Vo   |  |  |

| 11  | No Connect        | N.C. |  |  |

| 12  | EMI Shield [1]    | GND  |  |  |

FIGURE 1 Transceiver pin-out, top view

#### Note:

1. EMI Shield ground pins must be connected to the signal ground plane on the PCB. This is important to prevent cross-talk between Tx and Rx and also to shield the internal fiber optic transceivers (FOTs) from external EMI/EMC and ESD

2. For reduced power consumption and maximum operating lifetime, it is highly recommended to use a 3.3 V supply.

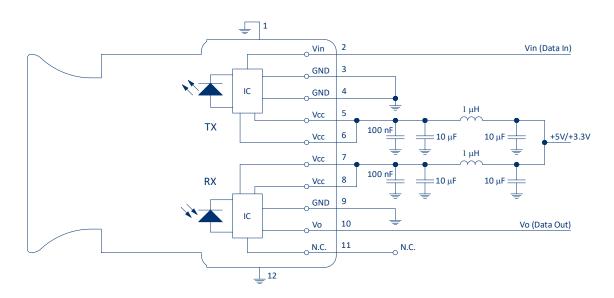

# **RECOMMENDED APPLICATION CIRCUIT**

FIGURE 2 Recommended application circuit

#### **GENERAL OPERATION**

# **Inverting Part FE50MKIR**

FE50MKIR consists of a non-inverting transmitter and inverting receiver.

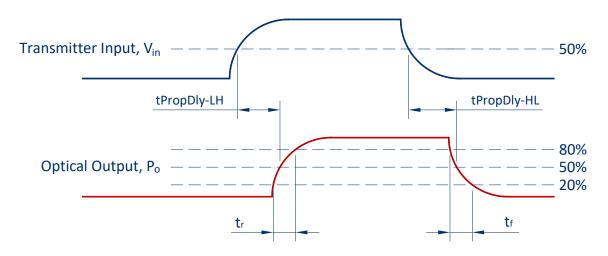

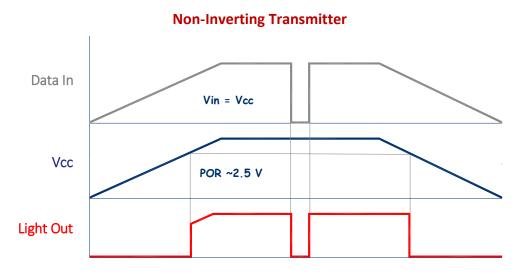

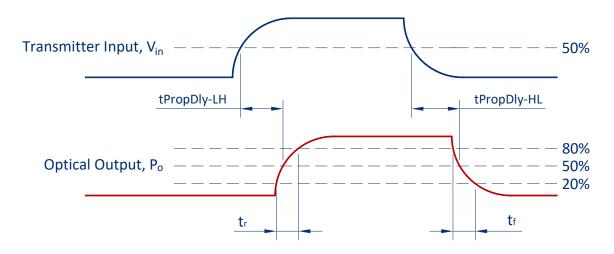

# **Non-Inverting Transmitter**

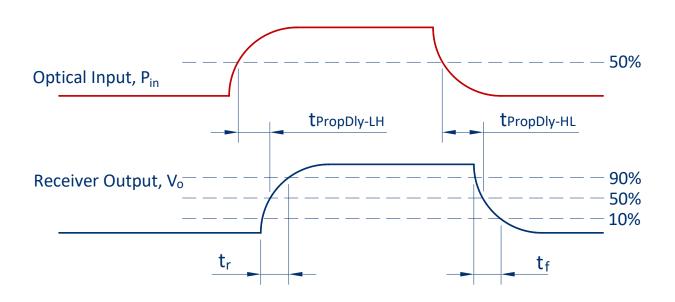

FIGURE 3

FE50MKIR Transmitter Propagation Delay and rise/fall time definitions

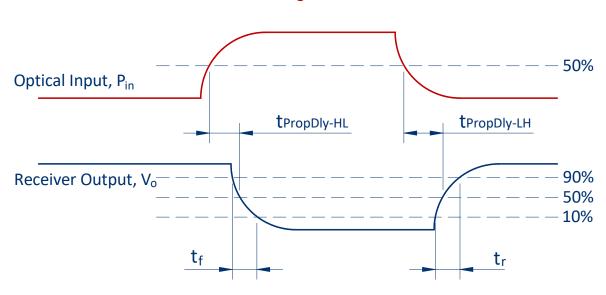

# **Inverting Receiver**

FIGURE 4

FE50MKIR Receiver Propagation Delay and rise/fall time definitions

# **Inverting Part FE50MKIR (Continued)**

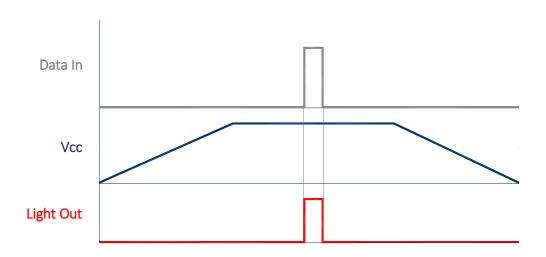

FE50MKIR operation during power up, power down or power reset is illustrated below in figures 5, 6 & 7.

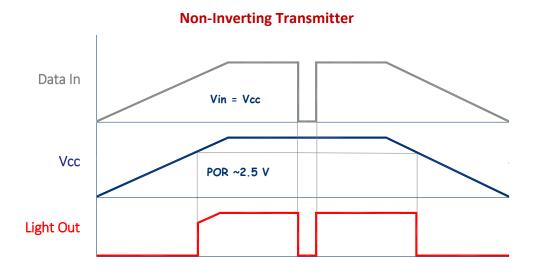

FIGURE 5

FE50MKIR Non-Inverting Tx operation during power cycling with input logic high

During power up as Vcc rises to approximately 2.5 V, there is no light output. Once Vcc reaches 2.5 V, the transmitter will output correctly based on the input voltage level. In Figure 5 above the input logic level is high during power up, so the transmitter will output light.

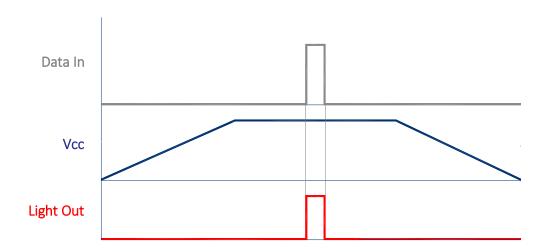

FIGURE 6

FE50MKIR Non-Inverting Tx operation during power cycling with input logic low

In Figure 6 the input logic level is low during power up, so the transmitter outputs no light.

# **Inverting Part FE50MKIR (Continued)**

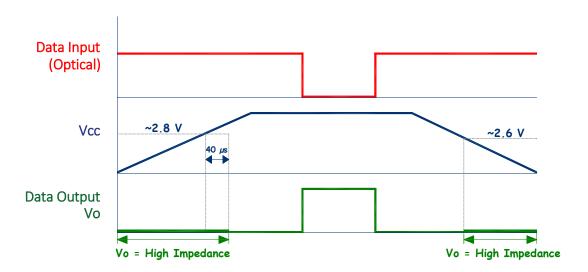

# **Inverting Receiver**

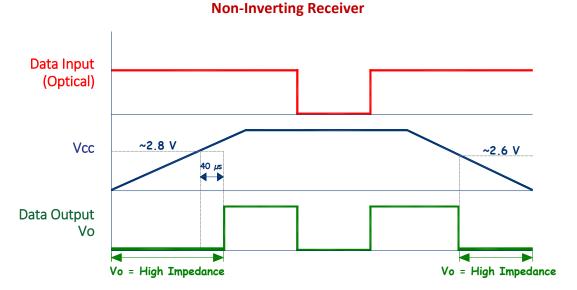

FIGURE 7

FE50MKIR Inverting Rx operation during power cycling

During power up as Vcc rises to approximately 2.8 V the output Vo is in a high impedance state. Within 40  $\mu$ s of Vcc reaching 2.8 V the output Vo will change to the correct logic state which in the diagram above is logic low as there is light present and the output is inverted relative to the light input. On power down once Vcc drops below approximately 2.6 V then Vo changes immediately to a high impedance state.

# **Non-Inverting Part FE50MKNR**

FE50MKIR consists of a non-inverting transmitter and non-inverting receiver.

# **Non-Inverting Transmitter**

FIGURE 8 FE50MKNR Transmitter Propagation Delay and rise/fall time definitions

# **Non-Inverting Receiver**

FIGURE 9 FE50MKNR Receiver Propagation Delay and rise/fall time definitions for a non-inverting  $V_{\text{o}}$  output

# Non-Inverting Part FE50MKNR (Continued)

FE50MKNR operation during power up, power down or power reset is illustrated below in figures 10, 11 & 12.

FIGURE 10 FE50MKNR Non-Inverting Tx operation during power cycling with input logic high

During power up as Vcc rises to approximately 2.5 V, there is no light output. Once Vcc reaches 2.5 V, the transmitter will output light correctly based on the input voltage level. In Figure 10 above the input logic level is high during power up, so the transmitter will output light.

FIGURE 11 FE50MKNR Non-Inverting Tx operation during power cycling with input logic low

In Figure 11 the input logic level is low during power up, so the transmitter outputs no light.

# Non-Inverting Part FE50MKNR (Continued)

FIGURE 12 FE50MKNR Non- Inverting Rx operation during power cycling

During power up as Vcc rises to approximately 2.8 V the output Vo is in a high impedance state. Within 40  $\mu$ s of Vcc reaching 2.8 V the output Vo will change to the correct logic state which in the diagram above is logic high as there is light present and the output is non-inverting. On power down once Vcc drops below approximately 2.6 V then Vo changes immediately to a high impedance state.

Table 4 **REGULATORY COMPLIANCE**

| Parameter                                                  | Symbol | Standard             | Level                  |

|------------------------------------------------------------|--------|----------------------|------------------------|

| Electrostatic Discharge,<br>Human Body Model (contact ESD) | НВМ    | JEDEC JS-001         | Level 2 (2kV to < 4kV) |

| UL Certification                                           | UL     | 60950-1              | Files No. Pending      |

| Storage Compliance                                         | MSL    | J-STD-020E           | 2a (4-week floor life) |

| Restriction of Hazardous<br>Substances Directive           | RoHS   | Directive 2011/65/EU | Certified compliant    |

| Eye Safety                                                 |        | IEC 60825-1          | LED Class 1            |

# Table 5 **ABSOLUTE MAXIMUM RATINGS**

These are the absolute maximum ratings at or beyond which the product can be expected to be damaged Notes:

- 1.

- 260 °C for 10 seconds, one time only, at least 2.2 mm away from lead root  $V_{IN}$  should not exceed Vcc. This is very important during the power-up sequence. If  $V_{IN}$  > Vcc, then the driver IC 2. power from  $V_{IN}$  to power-up. This is an uncontrolled logic state and must be avoided.

| Parameter                      | Symbol          | Minimum | Maximum | Unit |

|--------------------------------|-----------------|---------|---------|------|

| Storage Temperature            | $T_{stg}$       | -40     | +85     | °C   |

| Operating Temperature          | $T_{op}$        | -40     | +85     | °C   |

| Soldering Temperature [1]      | $T_{sld}$       |         | +260    | °C   |

| Supply Voltage (TX, RX)        | Vcc             | -0.5    | +5.5    | V    |

| TX Input Voltage (Data in) [2] | V <sub>IN</sub> | -0.5    | Vcc     | V    |

| RX Output Current              | I <sub>O</sub>  | -16     | +16     | mA   |

# Table 6 TRANSMITTER ELECTRICAL AND OPTICAL CHARACTERISTICS

#### Test Conditions:

- 1. Test data was validated over the full temperature range of -40 °C to +85 °C, and over both power supply rail options of 5 V and 3.3 V  $\pm$  5%. Typical data out is at 25 °C, with 50 Mbps PRBS data and 3.3 V Supply

- Output power levels are for peak (not average) optical output levels. For 50% duty cycle data, peak optical power is twice

the average optical power. Optical power is measured when coupled into 0.5 m of a 1 mm diameter 0.5 NA POF and a large

area detector.

- 3. Electrical input pulse width is determined at 1.5 V and dV/dt between 1 V and 2 V shall not be less than 1 V/ns.

- 4. Emission Wavelength (centroid)  $\lambda_c = \Sigma_i P_i$ .  $\lambda_i / \Sigma_i P_i$ . (Ref: EIA/TIA std. FOTP-127/6.1, 1991)

- 5. Spectral Width Root Mean Squared (RMS)  $\lambda_{RMS} = (\Sigma_i P_i (\lambda_c \lambda_i)^2 / \Sigma_i P_i)^{1/2}$ . (Ref. EIA/TIA std. FOTP-127/6.3, 1991)

- 6. Wake Up Delay is the time from valid power up to valid data output, at 5 V or 3.3 V +/-10%, with input data at 50% duty cycle

| Parameter                      | Symbol                  | Min  | Typical                   | Max        | Unit | Test Condition |

|--------------------------------|-------------------------|------|---------------------------|------------|------|----------------|

| Supply Current                 | Icc                     |      | 16.5 @ 3.3V<br>17.5 @ 5 V | 27         | mA   | [1]            |

| Input Voltage - Low            | $V_{IL}$                | -0.3 |                           | 0.8        | V    | [1]            |

| Input Voltage - High           | $V_{IH}$                | 2    |                           | Vcc + 0.25 | V    | [1]            |

| Data Input Capacitance         | C <sub>in</sub>         |      |                           | 7          | pF   |                |

| Data Input Resistance          | R <sub>in</sub>         | 10   |                           |            | ΜΩ   |                |

| Output Power                   | P <sub>High</sub>       | -9   |                           | -1         | dBm  | [1,2]          |

| Emission Wavelength (centroid) | $\lambda_{c}$           | 640  | 650                       | 680        | nm   | [4]            |

| Spectral Width (RMS)           | $\lambda_{RMS}$         |      |                           | 30         | nm   | [5]            |

| Optical Rise time (20% - 80%)  | t <sub>r</sub>          |      | 1.6                       | 5          | ns   | [1]            |

| Optical Fall time (20% - 80%)  | t <sub>f</sub>          |      | 1.3                       | 2          | ns   | [1]            |

| Propagation Delay Low-to-High  | t <sub>PropDly_LH</sub> | 13   | 22                        | 30         | ns   | [1], Figure 3  |

| Propagation Delay High-to Low  | t <sub>PropDly_HL</sub> | 13   | 22                        | 30         | ns   | [1], Figure 3  |

| TX Pulse Width Distortion      | PWD                     | -3   |                           | +3         | ns   | [1,4]          |

| Wake Up Delay (power up)       | t power-on              |      | 20                        |            | μs   | [6]            |

# Table 7 RECEIVER ELECTRICAL AND OPTICAL CHARACTERISTICS

#### Test Conditions:

- 1. Wake up Delay is the delay from VCC > 2.75 V to when the output will respond correctly to optical input. Output is held in tristate before this time.

- 2. Test data was validated using a transmitter with an emission wavelength between 635 and 680 nm with a 5ns rise and fall time, over the full temperature range of -40 °C to +85 °C, over both supply rail voltage options of 5 V and 3.3 V  $\pm$  10%, and over the input optical received power as specified by  $P_H$  and  $P_L$ . Input power levels are for peak (not average) optical input levels. For 50% duty cycle data, peak optical power is twice the average optical power. Data referred to as typical are rated at +25 °C

- 3. Optical signal from the recommended Transmitter circuit.

- 4. Testing in the recommended receiver circuit (RL= 50 k $\Omega$ , CL(total)= 15 pF)

- 5. PWD for Optical Input of 50 MBd, NRZ 27-1 (PRBS7) data, resulting in a BER  $\leq 10^{-9}$

- 6. PWD for 1st to 3rd pulse is characterized with minimum Optical Input pulse width of 20 ns, with the 1st pulse being the worst case. For pulses > 20 ns the PWD will be less. If data rate < 1 MBd, then the pulse width distortion = PWD 1st to 3rd pulse.

- 7. The performance of the receiver as given in Table 7 has been characterized for transmitters operating between 635 and 680 nm. The receiver will nevertheless respond to optical sources operating from the visible to near infra-red regions although the precise performance may differ from that given in Table 7 depending upon the precise wavelength and rise/fall time characteristics of the optical source used.

| Parameter                                             | Symbol                  | Min        | Typical | Max  | Unit | <b>Test Condition</b>             |

|-------------------------------------------------------|-------------------------|------------|---------|------|------|-----------------------------------|

| Supply Current                                        | I <sub>cc</sub>         |            | 20      | 25   | mA   | [2,3,4]                           |

| Wake Up Delay <sub>(power up)</sub>                   | t <sub>power-on</sub>   |            | 40      |      | μs   | [1]                               |

| High Level Output Voltage                             | V <sub>OH</sub>         | Vcc - 0.05 |         | Vcc  | V    | I <sub>OH-max</sub> = 40 uA, [2]  |

| Low Level Output Voltage                              | V <sub>OL</sub>         | 0          |         | 0.05 | V    | I <sub>OL-max</sub> = 1.6 mA, [2] |

| Optical Power High                                    | P <sub>H</sub>          | -22        |         | -1   | dBm  | [2,3]                             |

| Optical Power Low                                     | PL                      |            |         | -40  | dBm  | [2,3]                             |

| Data Rate                                             |                         | DC         |         | 50   | MBd  | Min UI = 20 ns,<br>Max f = 25 MHz |

| Output Rise Time (10% - 90%)                          | t <sub>r</sub>          |            |         | 6    | ns   | [2,3,4]                           |

| Output Fall Time (10% - 90%)                          | t <sub>f</sub>          |            |         | 6    | ns   | [2,3,4]                           |

| Pulse Width Distortion for PH range<br>-20 to + 2 dBm | PWD                     | -4         |         | 4    | ns   | [2,3,4,5]                         |

| Pulse Width Distortion for PH range<br>-20 to -22 dBm | PWD                     | -6         |         | 6    | ns   | [2,3,4,5]                         |

| Pulse Width Distortion<br>1st to 3rd pulse            | $PWD_{init}$            | -7         |         | 14   | ns   | [2,3,4,5,6]                       |

| Propagation Delay                                     | t <sub>PropDly-HL</sub> |            |         | 50   | ns   | [2,3,4]                           |

|                                                       | t <sub>PropDly-LH</sub> |            |         | 50   | ns   | [2,3,4]                           |

| Optical Sensitivity Range                             | $\lambda_{R}$           | 400        |         | 900  | nm   | [7]                               |

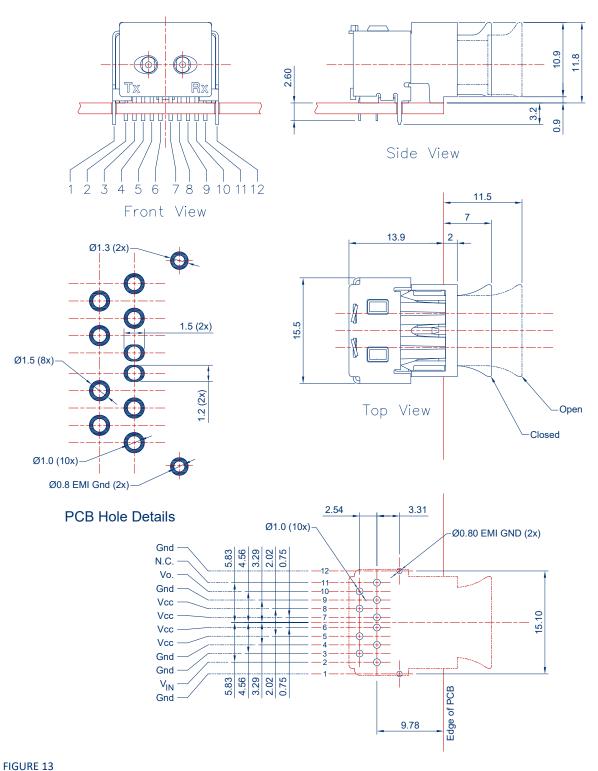

#### **MECHANICAL DATA**

Mechanical dimensions of the product, and PCB footprint, which is a top view General dimensional tolerance is  $\pm$  0.2 mm

NOTE: For PCB layout extra care is required with pin 6 and pin 7. On the PCB top and bottom metal they require a non-circular pad. The VIA's are standard plated circular through holes, however, the VIA top and bottom solder pad areas are non-circular 1.2 mm wide and 1.5 mm long oval shapes.

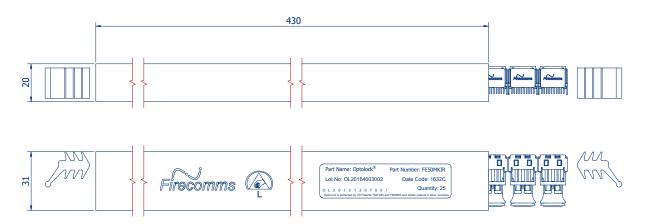

FIGURE 14

Packing tube for Firecomms FE50MKIR OptoLock® Transceivers

#### **PART HANDLING**

The transceivers are tested for handling in static-controlled assembly processes (HBM). Cleaning, degreasing and post solder washing should be carried out using standard solutions compatible with both plastics and the environment. For example, recommended solutions for degreasing are alcohols (methyl, isopropyl and isobutyl). Acetone, ethyl acetate, phenol or similar solution based products are not permitted.

In the soldering process, non-halogenated water soluble fluxes are recommended. These connectors are not suitable for use in reflow solder processes (infrared/vapor-phase reflow). The dust plug should remain in place during soldering, washing and drying processes to avoid contamination of the active optical area of each connector.

The Moisture Sensitivity Level (MSL) classification of this device is 2a according to JEDEC J-STD-020E. The shelf life of an unopened MBB (Moisture Barrier Bag) is 24 months at < 40 °C and < 90 % R.H. Once the Moisture Barrier Bag is opened the devices can be either

- a) Stored in normal factory conditions < 30 °C and < 60 % R.H. for a maximum of 672 hours (4 Weeks) prior to soldering.

- b) Stored at < 10 % R.H. (Dry Cabinet).

#### **PACKING INFORMATION**

Components are packed in PVC anti-static tubes in moisture barrier bags. Bags should be opened only in static-controlled locations, and standard procedures should be followed for handling moisture sensitive components.

| Components per Tube               |                     | 25      |

|-----------------------------------|---------------------|---------|

|                                   | Tube Length         | 430 mm  |

|                                   | Tube Width          | 31 mm   |

|                                   | Tube Height         | 20 mm   |

| Tubes per Bag                     |                     | 10      |

| Bags per Inner Carton             |                     | 1       |

|                                   | Inner Carton Length | 588 mm  |

|                                   | Inner Carton Width  | 147 mm  |

|                                   | Inner Carton Height | 84 mm   |

| Weight per Inner Carton, Complete |                     | 1.80 kg |

| Components per Inner Carton       |                     | 250     |

| Inner Cartons per Outer Carton    |                     | 4       |

|                                   | Outer Carton Length | 600 mm  |

|                                   | Outer Carton Width  | 310 mm  |

|                                   | Outer Carton Height | 195 mm  |

| Weight per Outer Carton, Complete |                     | 7.53 kg |

| Components per Outer Carton       |                     | 1000    |

For the most recent revision or further information please visit <a href="www.firecomms.com">www.firecomms.com</a> or contact the company directly at the following address, Firecomms Ltd, 2200 Airport Business Park, Cork, IRELAND. Copyright© 2004-2019 Firecomms. All rights reserved. Firecomms refers to Firecomms Limited and/or its subsidiaries. Firecomms assumes no responsibility for inaccuracies or omissions in the information contained in this document. Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein.